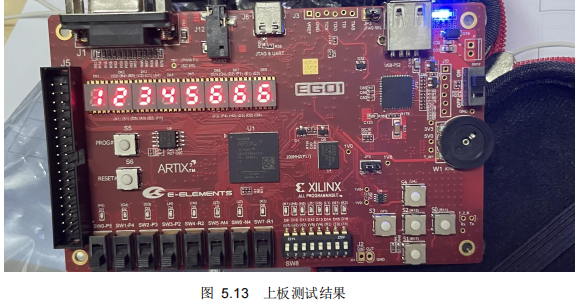

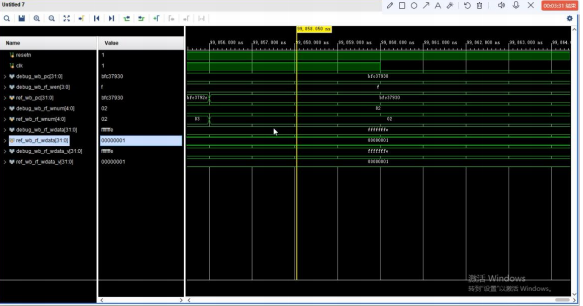

实现了基于 MIPS32I 指令集子集的 SOC 设计,该 SOC 系统支持 61 条指令, 6 种异常检测和消除,软中断,硬中断。实现了基于 trace 调试比对的测试框架,该框架作为 SOC 系统的测试平台, 同时也是 CPU 系统部件设计的测试平台。该测试框架利用已经开源的 GS132 处 理器,生成相应的测试数据,针对 PC 信号,寄存器数据信号,寄存器地址信 号,寄存器写信号进行比对,可以在有限时间内完成对 CPU 的仿真测试,大大 缩短测试周期实现了在 MIPS 处理器架构下显示模块的设计。MIPS 处理器中外设和存储 器采用 memory mapped 的形式,将外设和存储器地址空间共享,只需区分不同 地址,就可以针对性使用显示设备和存储器。同时,在该方法下,调用显示模 块的 IO 将简化为对存储器的访问形式,只需编写相应的汇编代码,就能调用 显示模块。

点击空白处退出提示

评论